Demonstration of Delay Line Memory on a Hardware Board

Delay Line Memory, a vintage technology, remains in use due to its novel design and principles. [P-Lab] has unveiled a demo board for delay-line memory, offering an intuitive demonstration of its workings through various visual aids.

For those unfamiliar, delay line memory is an outdated form of memory utilized in early computers such as the Univac-I and Olivetti Programma 101. It is a sequential-access technology, storing data as pulses on a medium and retrieving them in sequence. Variants of this technology were developed, like using acoustic pulses in mercury or torsional waves in coiled nickel wire.

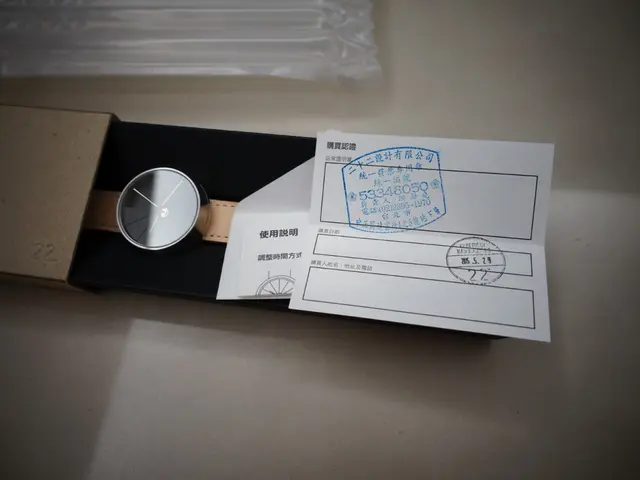

In this case, [P-Lab] has fabricated a solid-state delay line using TTL ICs, capable of storing 64 bits of data and capable of operating speeds up to 150 kHz. The board also incorporates a write-queuing system to ensure precise timing of data writes, due to the sequential nature of the technology that precludes random access. Moreover, it features LEDs to visually represent the memory's operation, including cycle indicators and LEDs for individual bits, combined with hexadecimal readouts for enhanced understanding.

[P-Lab] has previously showcased a similar approach with old-school core rope memory.

Special thanks to Giuseppe for this insightful tip.

This innovative demo board revives a classic memory technology while offering a unique illustration of digital logic design for educational purposes.

Related Details (if applicable):- Type: TTL-based digital delay line- Storage Capacity: 64 bits (8 bytes)- Speed: Up to 150 kHz- Visual Feedback: LED indicators (implied)

The DIY delayed-line memory demo board, a contemporary take on an old science and technology, showcases digital logic design with TTL-based components, storing 64 bits of data and capable of operating speeds up to 150 kHz. For those interested in the educational aspect, the board features LED indicators and hexadecimal readouts for a comprehensive understanding of its working mechanisms, similar to P-Lab's previous DIY core rope memory project.

![Ancient Delay Line Memory Technology Revisited: [P-Lab] Creates Demo Board Highlighting Its...](/en/img/20250529023718_pexels-search-image-description.jpeg)